## **DUAL POWER AMPLIFIER**

- SUPPLY VOLTAGE DOWN TO 3 V

- HIGH SVR

- LOW CROSSOVER DISTORTION

- LOW QUIESCENT CURRENT

- BRIDGE OR STEREO CONFIGURATION

#### **DESCRIPTION**

The TDA2824 is a monolithic integrated circuit in 12+2+2 powerdip, intended for use as dual audio power amplifier in portable radios and TV sets.

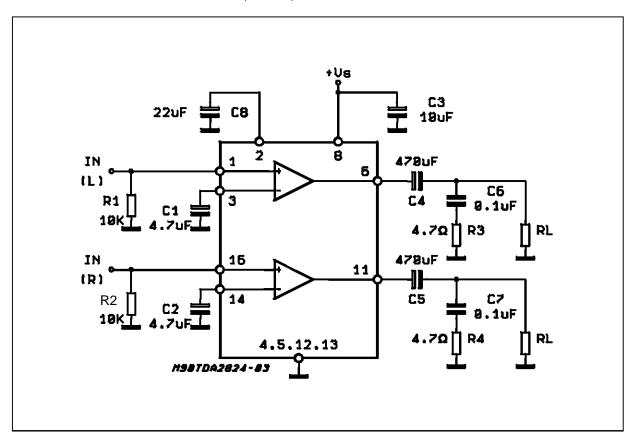

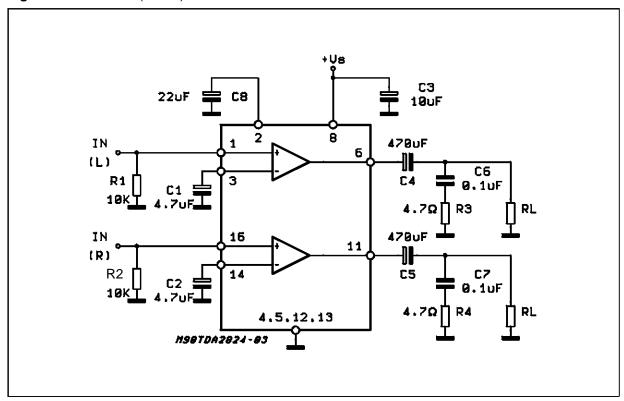

## TYPICAL APPLICATION CIRCUIT (Stereo)

January 1995 1/10

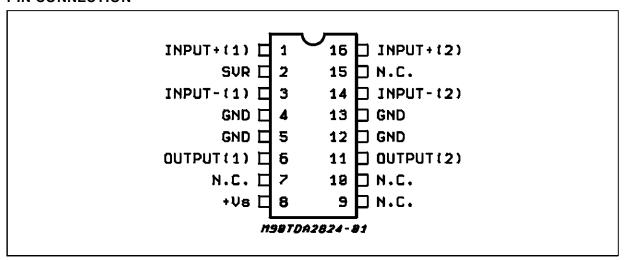

## **PIN CONNECTION**

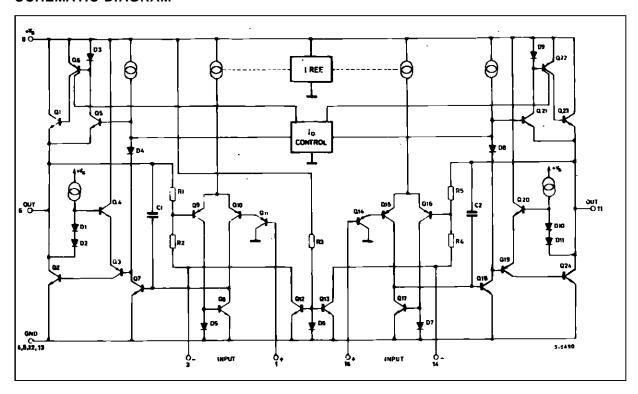

#### **SCHEMATIC DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol                            | Parameter                                                                     | Value      | Unit   |

|-----------------------------------|-------------------------------------------------------------------------------|------------|--------|

| Vs                                | Supply Voltage                                                                | 16         | V      |

| lo                                | Output Peak Current                                                           | 1.5        | Α      |

| P <sub>tot</sub>                  | Total Power Dissipation at $T_{amb} = 50^{\circ}C$<br>$T_{amb} = 70^{\circ}C$ | 1.25<br>4  | W<br>W |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and Junction Temperature                                              | -40 to 150 | °C     |

## **THERMAL DATA**

| Symbol                 | Parameter                                | Value | Unit |

|------------------------|------------------------------------------|-------|------|

| R <sub>th j-amb</sub>  | Thermal Resistance Junction-ambient Max. | 80    | °C/W |

| R <sub>th j-case</sub> | Thermal Resistance Junction-case Max.    | 20    | °C/W |

# **ELECTRICAL CHARACTERISTICS** ( $V_S = 6V$ , $T_{amb} = 25$ °C, unless otherwise specified)

| Symbol                          | Parameter                | Test Conditions                            | Min. | Тур.     | Max. | Unit   |  |

|---------------------------------|--------------------------|--------------------------------------------|------|----------|------|--------|--|

| STEREO (test circuit of fig. 1) |                          |                                            |      |          |      |        |  |

| Vs                              | Supply Voltage           |                                            | 3    |          | 15   | V      |  |

| Vo                              | Quiescent Output Voltage | V <sub>S</sub> = 9V<br>V <sub>S</sub> = 9V |      | 4<br>2.7 |      | V<br>V |  |

| Vo             | Quiescent Output Voltage       | $V_S = 9V$<br>$V_S = 9V$                                  |                   | 4<br>2.7    |                     | V<br>V |             |

|----------------|--------------------------------|-----------------------------------------------------------|-------------------|-------------|---------------------|--------|-------------|

| I <sub>d</sub> | Quiescent Drain Current        |                                                           |                   |             | 6                   | 12     | mA          |

| I <sub>b</sub> | Input Bias Current             |                                                           |                   |             | 100                 |        | nA          |

| Po             | Output Power<br>(each channel) |                                                           |                   | 1.3<br>0.45 | 1.7<br>0.65<br>0.32 |        | W<br>W<br>W |

| d              | Distortion                     | $V_S = 9V$ , $f = 1KHz$<br>$R_L = 8\Omega$ , $P_O = 0.5W$ |                   |             | 0.2                 |        | %           |

| G <sub>V</sub> | Closed Loop Voltage<br>Gain    | f = 1KHz                                                  |                   | 36          | 39                  | 41     | dB          |

| Ri             | Input Resistance               | f = 1KHz                                                  |                   | 100         |                     |        | ΚΩ          |

| e <sub>N</sub> | Total Input Noise              | $R_S = 10K\Omega$                                         | B = 22Hz to 22KHz |             | 2.5                 |        | μV          |

|                |                                |                                                           | Curve A           |             | 2                   |        | μV          |

| SVR            | Supply Voltage Rejection       | f = 100Hz                                                 |                   | 40          | 50                  |        | dB          |

| CS             | Channel Separation             | $R_S = 10K\Omega$ $f = 1KHz$                              |                   |             | 50                  |        | dB          |

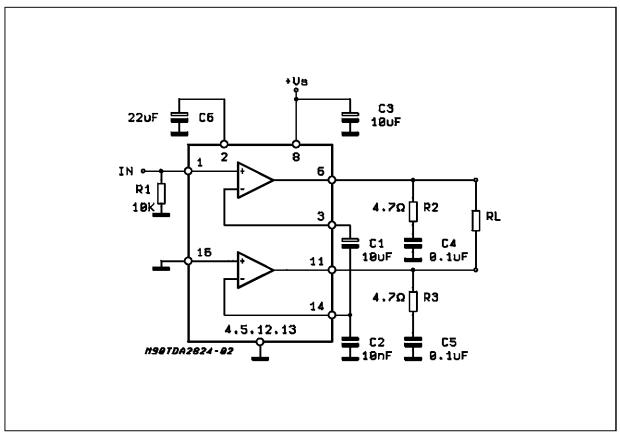

# BRIDGE (test circuit of fig. 2)

| Vs             | Supply Voltage              |                                                                                |                                                            | 3          |                  | 15 | V           |

|----------------|-----------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------|------------|------------------|----|-------------|

| Vos            | Output Offset Voltage       | $R_1 = 8\Omega$                                                                |                                                            | <b> </b>   |                  | 60 | mV          |

| I <sub>b</sub> | Imput Bias Current          |                                                                                |                                                            |            | 100              |    | nA          |

| Po             | Output Power                | d = 10%<br>V <sub>S</sub> = 9V<br>V <sub>S</sub> = 6V<br>V <sub>S</sub> = 4.5V | $f = 1KHz$ $R_L = 8\Omega$ $R_L = 8\Omega$ $R_L = 4\Omega$ | 2.5<br>0.9 | 3.2<br>1.35<br>1 |    | W<br>W<br>W |

| d              | Distortion (f = 1KHz)       | $R_L = 8\Omega$                                                                | P <sub>O</sub> = 0.5W                                      |            | 0.2              |    | %           |

| Gv             | Closed Loop Voltage<br>Gain | f = 1KHz                                                                       |                                                            |            | 39               |    | dB          |

| e <sub>N</sub> | Total Input Noise           | R <sub>S</sub> = 10KΩ                                                          | B = 22Hz to 22KHz                                          |            | 3                |    | mV          |

|                |                             |                                                                                | Curve A                                                    |            | 2.5              |    | μV          |

| SVR            | Supply Voltage Rejection    | f = 100Hz                                                                      |                                                            | 48         | 60               |    | dB          |

Figure 1: Test Circuit (stereo).

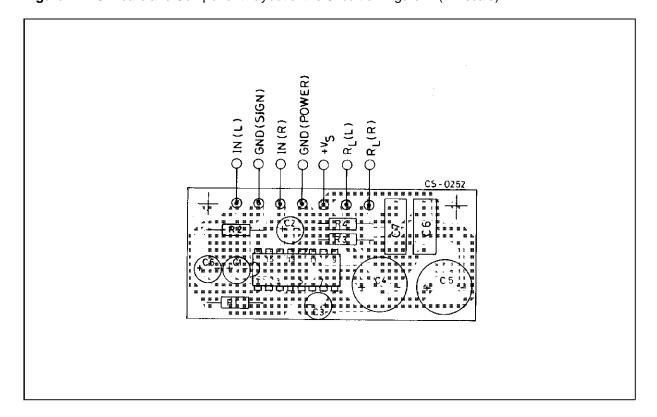

Figure 2: P.C. Board and Component Layout of the Circuit of Figure 1. (1:1 scale)

Figure 3: Test Circuit (bridge).

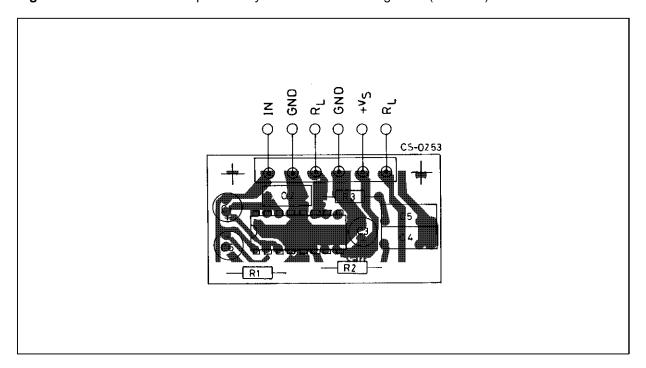

Figure 4: P.C. Board and Component Layout of the Circuit of Figure 3. (1:1 scale)

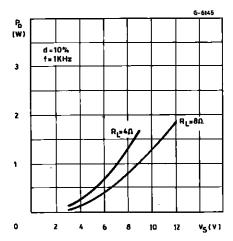

Figure 3 : Output Power vs. Supply Voltage (Stereo).

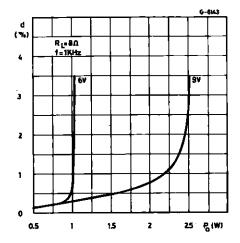

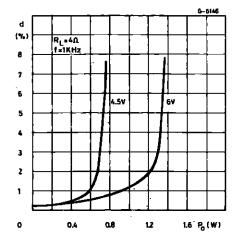

Figure 5: Distortion vs. Output Power (Bridge).

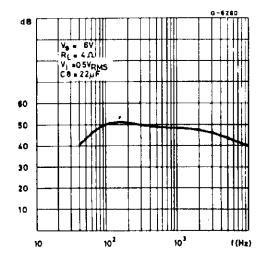

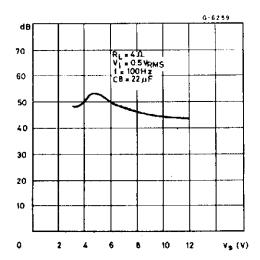

**Figure 7 :** Supply Voltage Rejection vs. Frequency (Stereo)

**Figure 4 :** Output Power vs. Supply Voltage (Bridge).

Figure 6 : Distortion vs. Output Power (Bridge).

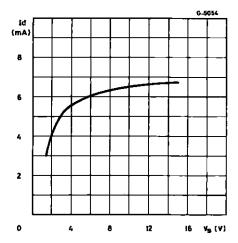

Figure 8 : Quiescent Current vs. Supply Voltage.

Figure 9: Quiescent Current vs. Supply Voltage.

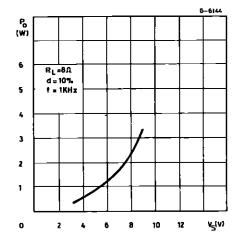

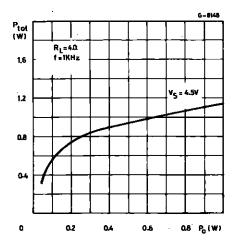

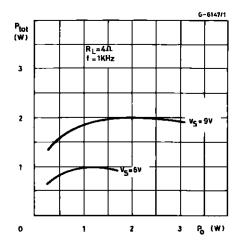

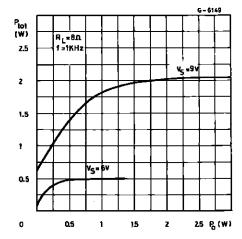

**Figure 11 :** Total Power Dissipation vs. Output Power (Bridge).

**Figure 10 :** Total Power Dissipation vs. Output Power (Stereo).

**Figure 12 :** Total Power Dissipation vs. Output Power (Bridge).

#### MOUNTING INSTRUCTION

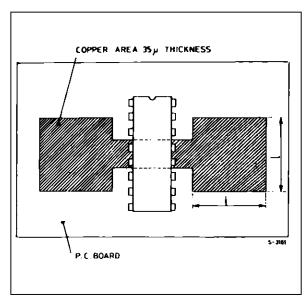

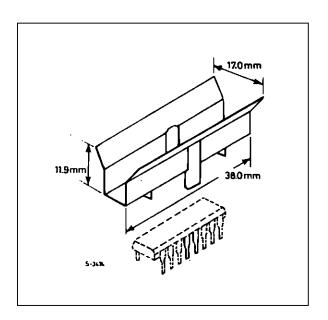

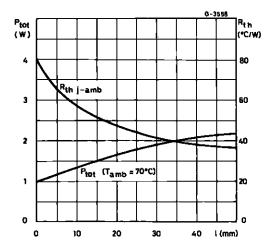

The R<sub>th j-amb</sub> of the TDA2824 can be reduced by soldering the GND pins to a suitable copper area of the printed circuit board (Figure 13) or to an external heatsink (Figure 14).

The diagram of Figure 15 shows the maximum dissipable power  $P_{tot}$  and the  $R_{th\,j\text{-amb}}$  as a function of the side " $\partial$ " of two equal square copper areas having a thickness of 35  $\mu$  (1.4 mils).

**Figure 13 :** Example of P.C. Board Copper Area which is used as Heatsink.

During soldering the pins temperature must not exceed 260 °C and the soldering time must not be longer than 12 seconds.

The external heatsink or printed circuit copper area must be connected to electrical ground.

**Figure 14:** External Heatsink Mounting Example.

Figure 15: Maximum Dissipable Power and Junction to Ambient Thermal Resistance vs. Side "∂".

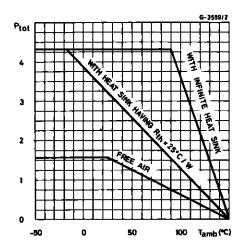

**Figure 16 :** Maximum Allowable Power Dissipation vs. Ambient Temperature.

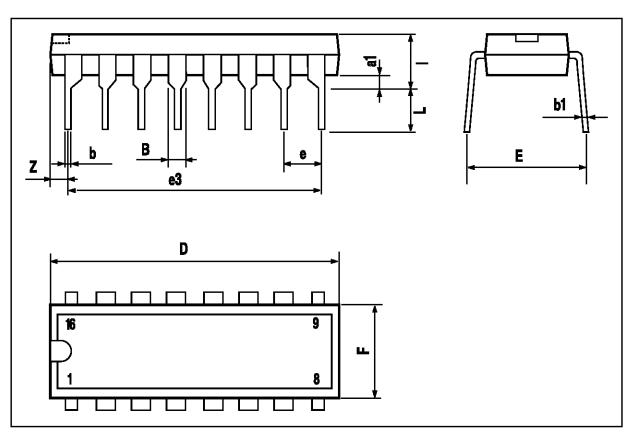

## POWERDIP 12+2+2 PACKAGE MECHANICAL DATA

| DIM. | mm   |       |      | inch  |       |       |  |

|------|------|-------|------|-------|-------|-------|--|

|      | MIN. | TYP.  | MAX. | MIN.  | TYP.  | MAX.  |  |

| a1   | 0.51 |       |      | 0.020 |       |       |  |

| В    | 0.85 |       | 1.40 | 0.033 |       | 0.055 |  |

| b    |      | 0.50  |      |       | 0.020 |       |  |

| b1   | 0.38 |       | 0.50 | 0.015 |       | 0.020 |  |

| D    |      |       | 20.0 |       |       | 0.787 |  |

| E    |      | 8.80  |      |       | 0.346 |       |  |

| е    |      | 2.54  |      |       | 0.100 |       |  |

| e3   |      | 17.78 |      |       | 0.700 |       |  |

| F    |      |       | 7.10 |       |       | 0.280 |  |

| I    |      |       | 5.10 |       |       | 0.201 |  |

| L,   |      | 3.30  |      |       | 0.130 |       |  |

| Z    |      |       | 1.27 |       |       | 0.050 |  |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1995 SGS-THOMSON Microelectronics - All Rights Reserved

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thaliand - United Kingdom - U.S.A.